Technische Informatik

Speicher

Thorsten Thormählen

15. Dezember 2022

Teil 8, Kapitel 1

Thorsten Thormählen

15. Dezember 2022

Teil 8, Kapitel 1

Dies ist die Druck-Ansicht.

Weiterschalten der Folien durch die → Taste oder

durch das Klicken auf den rechten Folienrand.

Das Weiterschalten der Folien kann ebenfalls durch das Klicken auf den rechten bzw. linken Folienrand erfolgen.

| Typ | Schriftart | Beispiele |

|---|---|---|

| Variablen (Skalare) | kursiv | $a, b, x, y$ |

| Funktionen | aufrecht | $\mathrm{f}, \mathrm{g}(x), \mathrm{max}(x)$ |

| Vektoren | fett, Elemente zeilenweise | $\mathbf{a}, \mathbf{b}= \begin{pmatrix}x\\y\end{pmatrix} = (x, y)^\top,$ $\mathbf{B}=(x, y, z)^\top$ |

| Matrizen | Schreibmaschine | $\mathtt{A}, \mathtt{B}= \begin{bmatrix}a & b\\c & d\end{bmatrix}$ |

| Mengen | kalligrafisch | $\mathcal{A}, B=\{a, b\}, b \in \mathcal{B}$ |

| Zahlenbereiche, Koordinatenräume | doppelt gestrichen | $\mathbb{N}, \mathbb{Z}, \mathbb{R}^2, \mathbb{R}^3$ |

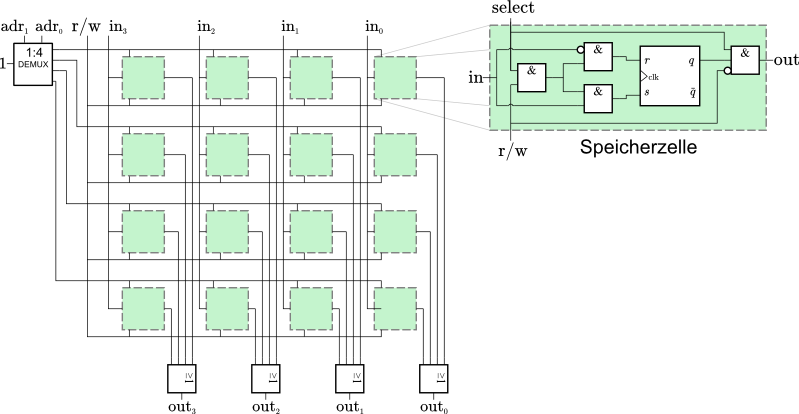

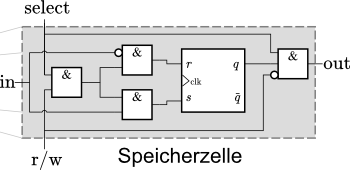

| $\text{select}$ | $\text{r/w}$ | $\text{in}$ | $\text{out}$ | $q^{t+1}$ |

| 0 | × | × | 0 | $q^t$ |

| 1 | 0 | 0 | $q^t$ | $q^t$ |

| 1 | 0 | 1 | $q^t$ | $q^t$ |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 1 |

| Jahr der Einführung | Größe | Preis pro MB | Zugriffszeit neue Zeile bzw. Spalte | Zugriffszeit gleiche Zeile |

|---|---|---|---|---|

| 1980 | 64 KB | 1500 USD | 250 ns | 150 ns |

| 1983 | 256 KB | 500 USD | 185 ns | 100 ns |

| 1985 | 1 MB | 200 USD | 135 ns | 40 ns |

| 1989 | 4 MB | 50 USD | 110 ns | 40 ns |

| 1992 | 16 MB | 15 USD | 90 ns | 30 ns |

| 1996 | 64 MB | 10 USD | 60 ns | 12 ns |

| 1998 | 128 MB | 4 USD | 60 ns | 10 ns |

| 2000 | 256 MB | 1 USD | 55 ns | 7 ns |

| 2002 | 512 MB | 0,25 USD | 50 ns | 5 ns |

| 2004 | 1 GB | 0,10 USD | 45 ns | 3 ns |

| 2012 | 8 GB | 0,01 USD | 24 ns | 0,25 ns |

Anregungen oder Verbesserungsvorschläge können auch gerne per E-mail an mich gesendet werden: Kontakt